### COMMUNICATIONS CACM.ACM.ORG OF THE ACM OF THE ACM

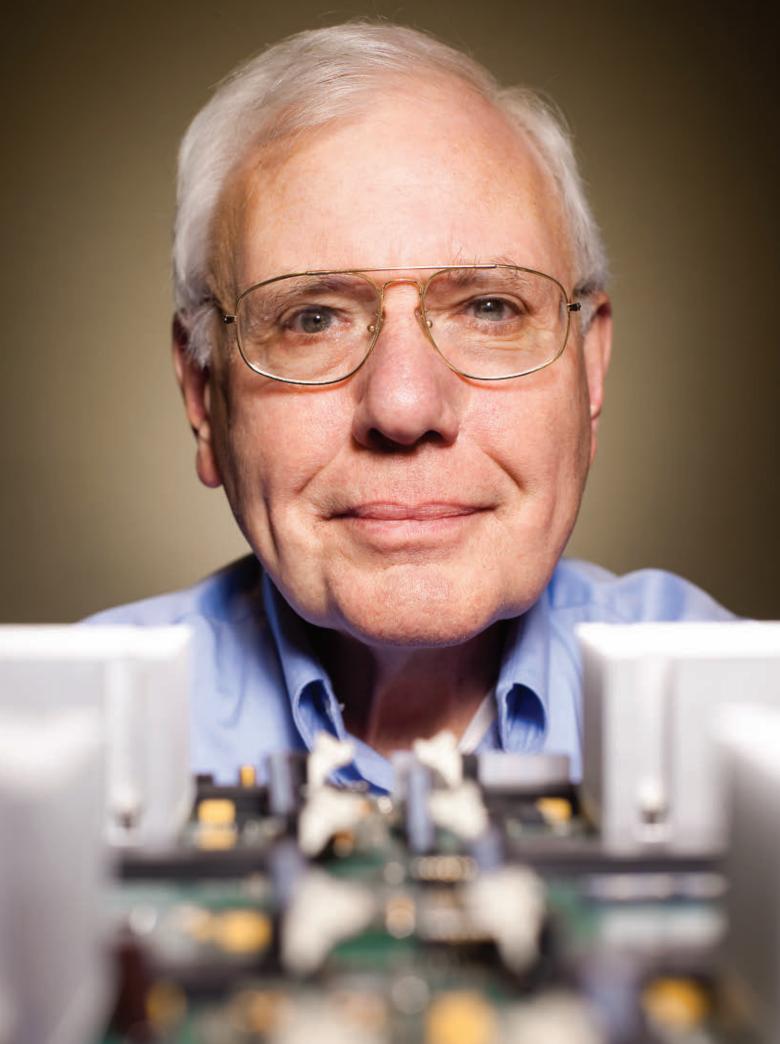

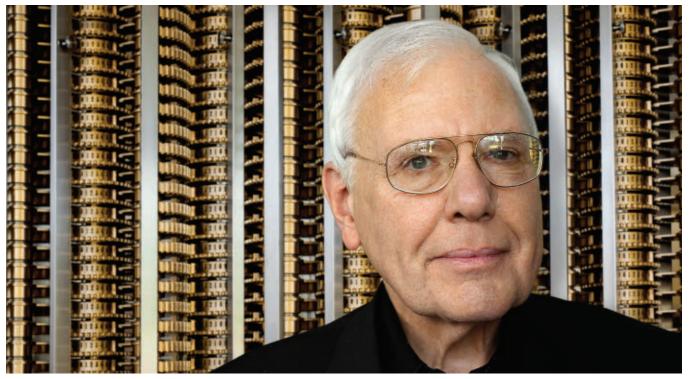

# **Charles P. Thacker** ACM's A.M. Turing Award Winner

### 25TH IEEE International Parallel and Distributed Processing Symposium

May 16-20, 2011 • Anchorage (Alaska) • USA

Embraced by six mountain ranges, with views of Mount McKinley in Denali National Park, and warmed by a maritime climate, Anchorage offers year-round adventure and recreation. It is a fitting destination for IPDPS to mark a quarter century of tracking developments in computer science. To celebrate the 25th year of IPDPS, plan to come early and stay late to enjoy a modern city surrounded by spectacular wilderness.

GENERAL CHAIR

Alan Sussman (University of Maryland, USA)

PROGRAM CHAIR Frank Mueller (North Carolina State University, USA)

PROGRAM VICE-CHAIRS ALGORITHMS: Olivier Beaumont (INRIA, France) APPLICATIONS: Leonid Oliker (Lawrence Berkeley National Laboratory, USA)

ARCHITECTURES: Mahmut Taylan Kandemir (The Pennsylvania State University, USA)

SOFTWARE: Dimitrios S. Nikolopoulos (FORTH-ICS and University of Crete, Greece)

WORKSHOPS CHAIR Ümit V. Çatalyürek (Ohio State University, USA)

PhD FORUM CHAIR Luc Bougé (ENS Cachan, France)

#### **STEERING CO-CHAIRS**

Viktor K. Prasanna (University of Southern California, USA) George Westrom (Discovery Science Center & FSEA, USA)

#### CALL FOR PARTICIPATION

In addition to the regular conference program of contributed papers, invited speakers and panels, PhD forum, and tutorials, IPDPS features workshops on the first and last days of the conference. Watch the IPDPS Web for updates and information on how to participate in all events.

Committee on Parallel Processing.

In cooperation with ACM SIGARCH, IEEE Computer Society Technical Committee on Computer Architecture, and IEEE Computer Society Technical Committee on Distributed Processing.

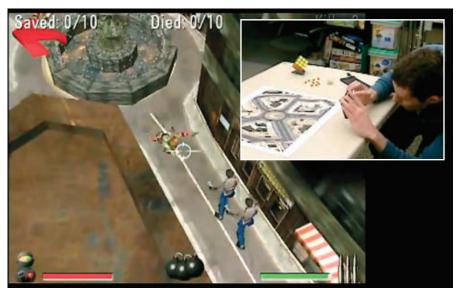

### **CALL FOR PAPERS**

Scope: Authors are invited to submit manuscripts that present original unpublished research in all areas of parallel and distributed processing, including the development of experimental or commercial systems. Work focusing on emerging technologies is especially welcome. Topics of interest include, but are not limited to:

- Parallel and distributed algorithms, focusing on issues such as: stability, scalability, and fault-tolerance of algorithms and data structures for parallel and distributed systems, communication and synchronization protocols, network algorithms, scheduling, and load balancing.

- Applications of parallel and distributed computing, including web applications, peer-to-peer computing, cloud and grid computing, scientific applications, and mobile computing. Papers focusing on applications using novel commercial or research architectures, or discussing scalability toward the exascale level are encouraged.

- Parallel and distributed architectures, including architectures for instruction-level and thread-level parallelism; petascale and exascale systems designs; special-purpose architectures, including graphics processors, signal processors, network processors, media accelerators, and other special purpose processors and accelerators; impact of technology on architecture; network and interconnect architectures; parallel I/O and storage systems; architecture of the memory hierarchy; power-efficient architectures; dependable architectures; and performance modeling and evaluation.

- Parallel and distributed software, including parallel and multicore programming languages and compilers, runtime systems, operating systems, resource management, middleware for grids and clouds, libraries, performance modeling and evaluation, parallel programming paradigms, and programming environments and tools.

Best Papers Awards: Awards will be given for one best paper in each of the four conference technical tracks: algorithms, applications, architectures, and software. Selected papers will be considered for possible publication in a special issue of the Journal of Parallel and Distributed Computing.

What/Where to Submit: More details on submissions and instructions for submitting files are available at www.ipdps.org or may be obtained by sending email to cfp@ipdps.org for an automatic reply. IPDPS will again require submission of abstracts one week before the paper submission deadline without any late exceptions (see important dates). All submitted manuscripts will be reviewed. Submitted papers may NOT have appeared in, or be under consideration for, another conference or workshop, or for a journal.

# 2011 ANCHORAGE

www.ipdps.org

| IMPORTANT DATES |                                               |  |  |

|-----------------|-----------------------------------------------|--|--|

| 24 September    | 2010 Abstracts due(required)                  |  |  |

| 1 October 2010  | Submissions due(hard deadline, no extensions) |  |  |

| 10-12 November  | Rebuttal period                               |  |  |

| 17 December     | Author notification                           |  |  |

| 1 February 2011 | Camera-ready papers                           |  |  |

### springer.com

# **Noteworthy Titles**

#### Practitioners

**C. Paar**, **J. Pelzl**, Ruhr-Universität Bochum, Germany

Understanding

Cryptography

A Textbook for

Students and

#### Foreword by: B. Preneel

Uniquely designed for students of engineering and applied computer science, and engineering practitioners. The authors have considerable experience teaching applied cryptography to engineering and computer science students and to professionals, and they make extensive use of examples, problems, and chapter reviews, while the book's website offers slides, projects and links to further resources.

1st Edition. 2nd Printing 2010. XVIII, 372 p. 320 illus., 160 in color. Hardcover ISBN 978-3-642-04100-6 ► **\$49.95**

#### Handbook of Ambient Intelligence and Smart Environments

**H. Nakashima**, Future University, Hakodate, Hokkaido, Japan;

H. Aghajan, Stanford University, Stanford, CA, USA; J. C. Augusto, University of Ulster at Jordanstown, Newtownabbey, UK (Eds.)

Provides readers with comprehensive, up-todate coverage in this emerging field. Organizes all major concepts, theories, methodologies, trends and challenges into a coherent, unified repository. Covers a wide range of applications relevant to both ambient intelligence and smart environments. First available reference into this emerging area of research.

2010. XVIII, 1294 p. 100 illus. Hardcover ISBN 978-0-387-93807-3 ► **\$229.00**

#### Introduction to Databases From Biological to Spatio-Temporal

**P. Revesz**, University of Nebraska-Lincoln, Lincoln, NE, USA

Provides a comprehensive coverage of the field of databases. This textbook reveals the workings of numerous database systems, enabling readers to develop complex database applications. Students will gain hands-on experience by following the exercises. The theory is complemented by detailed examination of specific applications from a broad range of areas.

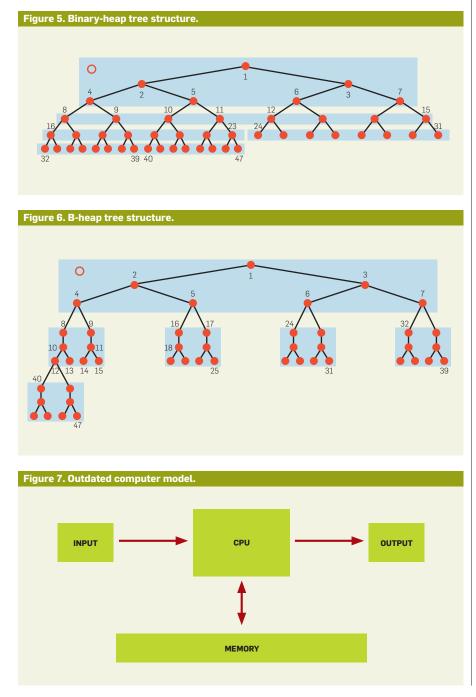

2010. XVIII, 754 p. 346 illus., 173 in color. (Texts in Computer Science) Hardcover ISBN 978-1-84996-094-6 ► **\$119.00**

Munich, Germany

#### Patent Law for Computer Scientists

Steps to Protect Computer-Implemented Inventions

D. Closa, A. Gardiner, F. Giemsa, J. Machek, European Patent Office,

Explains patent laws in Europe, the US, and Japan. Gives the reader a guide to a patent examiner's way of thinking. Shows the step-bystep development of a patent application. Presents more than 10 detailed case studies from different computer science applications. Condenses over 70 years experience of the authors in the patent business.

2010. XV, 194 p. Hardcover ISBN 978-3-642-05077-0 ► **\$49.95**

#### Requirements Engineering

K. Pohl, Universität Duisburg-Essen,

Germany

Most comprehensive description of requirements engineering (RE) foundations and principles as well as up-to-date techniques, such as goal-oriented RE and scenario-based RE. Presentation of a didactically sound and industrially validated framework to structure the RE process and procedures. Many checklists and guidelines to support readers in their application of the concepts presented.

2010. 1050 p. Hardcover ISBN 978-3-642-12577-5 ► **\$79.95**

#### Algorithmic Adventures

From Knowledge to Magic

J. Hromkovic, ETH Zentrum, Zürich, Switzerland Good explanation of

even the most basic techniques. Demonstrates the power and magic of the underlying principles. Fascinating read for students of all levels and for those curious to learn about the science and magic of algorithmics

2009. XIII, 363 p. Hardcover ISBN 978-3-540-85985-7 ► **\$59.95**

Easy Ways to Order for the Americas ► Write: Springer Order Department, PO Box 2485, Secaucus, NJ 07096-2485, USA ► Call: (toll free) 1-800-SPRINGER ► Fax: 1-201-348-4505 ► Email: orders-ny@springer.com or for outside the Americas ► Write: Springer Customer Service Center GmbH, Haberstrasse 7, 69126 Heidelberg, Germany ► Call: +49 (0) 6221-345-4301 ► Fax: +49 (0) 6221-345-4229 ► Email: orders-hd-individuals@springer.com ► Prices are subject to change without notice. All prices are net prices.

# COMMUNICATIONS OF THE ACM

#### **Departments**

- 5 Editor's Letter Hypercriticality By Moshe Y. Vardi

- 6 Letters To The Editor Don't Ignore Security Offshore, or in the Cloud

#### 9 In the Virtual Extension

#### 10 BLOG@CACM

Software Development and Crunch Time; and More Ruben Ortega discusses developers and crunch time; Mark Guzdial on the impact of open source practices on computing education; and Daniel Reed on the shift from computational paucity to computational plethora.

12 CACM Online

In Case You Missed It By David Roman

- 39 **Calendar**

- 107 Careers

#### Last Byte

112 Q&A

**From Single Core to Multicore** Charles P. Thacker discusses the legendary Alto personal computer, the invention of the Ethernet, and his current research on multicore architectures. *By Leah Hoffmann*

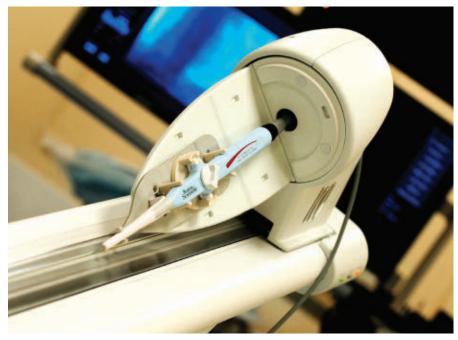

Charles P. Thacker. ACM's 2009 A.M. Turing Award winner, as photographed by Richard Morgenstein in the data center of Microsoft's offices in Mountain View, CA. For more on Morgenstein's work, see http://www. morgenstein.com.

About the Cover:

#### News

- 13 **Sharing Computational Perspectives** Computer scientists are now making intellectual contributions to a wide range of other disciplines, including evolutionary theory, physics, and economics. *By David Lindley*

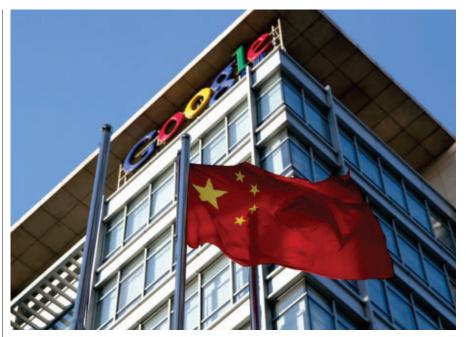

- 16 Censored!

Countries use Internet censorship to dominate the political dialogue, but also to create favorable conditions for government-controlled businesses. *By Samuel Greengard*

19 Mainstreaming Augmented Reality Advancements in computer vision, object recognition, and related technologies are leading to new levels of sophistication in augmented-reality applications, and presenting new ways for humans to relate to the natural world. By Kirk L. Kroeker

22 **Committed to Success** Charles P. Thacker discusses the importance of simplicity, reusable tools, thinking broadly, and his practice of Tom Sawyering. *By Gary Anthes*

24 **Eric Brewer: Change Agent** Eric Brewer's latest project involves designing and deploying low-cost wireless infrastructure in developing regions. *By Gregory Goth*

25 **Visions of the Future** ACM joined forces with the British Computer Society to deliver its first academic research conference in Europe. *By Sarah Underwood*

#### Viewpoints

- 27 Technology Strategy and Management Outsourcing Versus Shared Services Choosing between outsourcing and shared services has significant implications for long-term corporate strategy. By Mari Sako

- 30 **Computing Ethics Work Life in the Robotic Age** Technological change results in changes in expectations, in this case affecting the workplace. *By Jason Borenstein*

- 32 Legally Speaking Should the Google Book Settlement Be Approved? Considering the precedent that could be established by approval of the controversial Google book settlement. By Pamela Samuelson

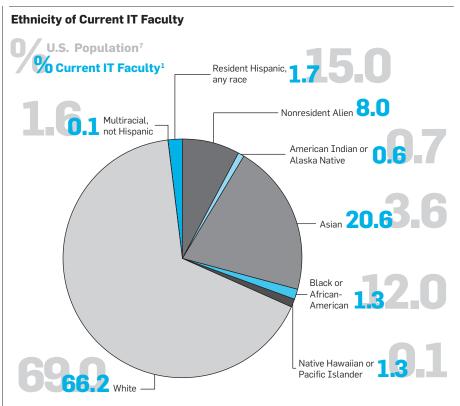

- Broadening Participation

Cultivating Cultural Diversity

in Information Technology

Introducing CMD-IT, a new center focused on synergistic activities

related to ethnic minorities and people with disabilities.

By Valerie E. Taylor

- 37 Viewpoint

Is Computer Science Truly Scientific? Reflections on the (experimental) scientific method in computer science. By Gonzalo Génova

40 Distinguished Members Advice to Members Seeking ACM Distinction By Marc Snir and Telle Whitney

### 07/2010 VOL. 53 NO. 07

#### Practice

- 42 **The Ideal HPC Programming Language** Maybe it's Fortran. Or maybe it just doesn't matter. *By Eugene Loh*

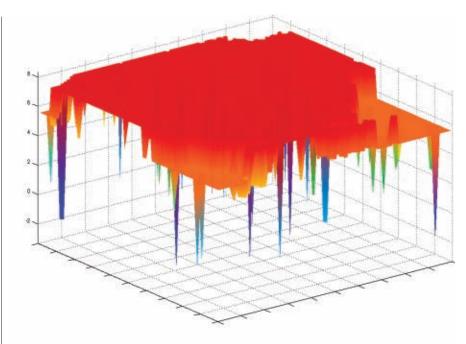

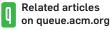

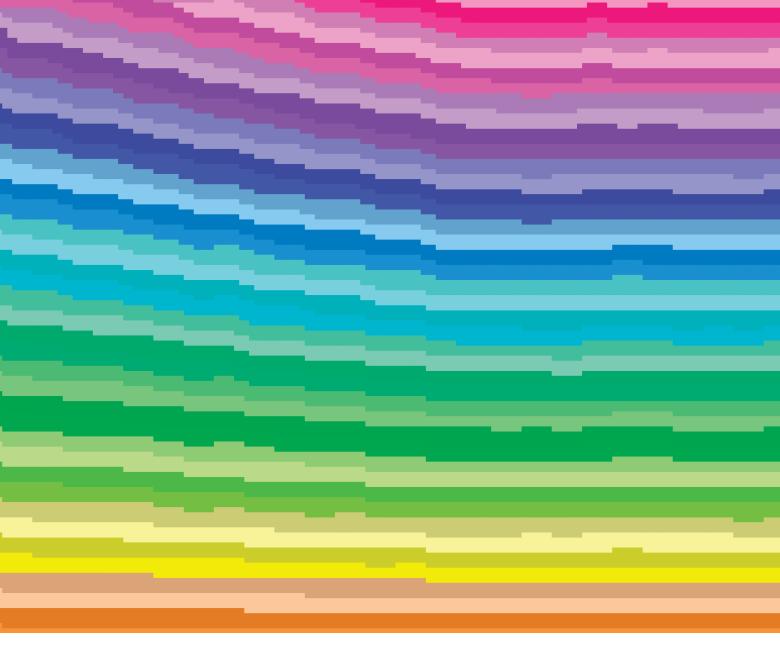

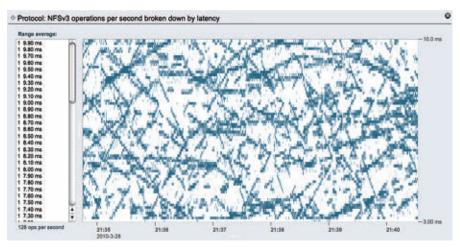

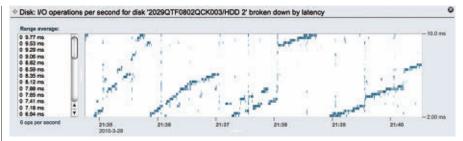

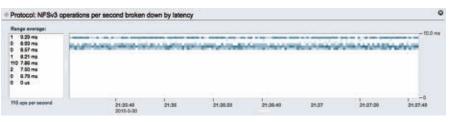

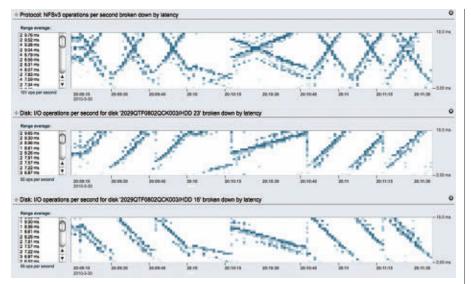

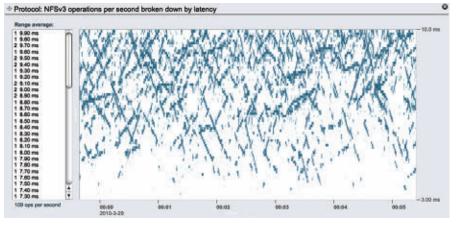

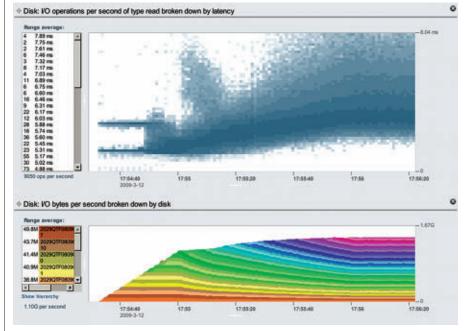

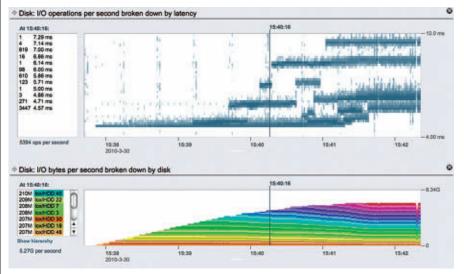

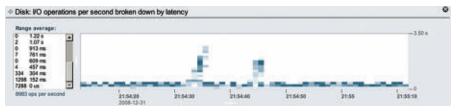

- Visualizing System Latency

Heat maps are a unique and powerful way to visualize latency data.

Explaining the results, however, is an ongoing challenge.

By Brendan Gregg

- 55 You're Doing It Wrong Think you've mastered the art of server performance? Think again. By Poul-Henning Kamp

Articles' development led by **CCMQUEUE** queue.acm.org

#### **Review Articles**

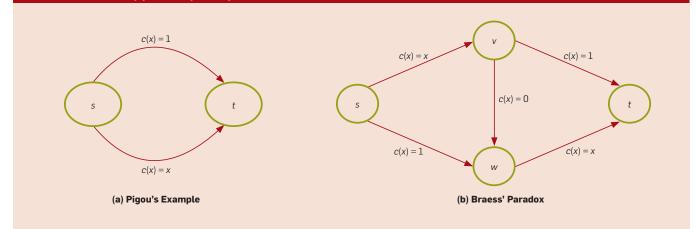

78 Algorithmic Game Theory

A new era of theoretical computer science addresses fundamental problems about auctions, networks, and human behavior.

By Tim Roughgarden

#### **Contributed Articles**

60 Commonsense Understanding of Concurrency: Computing Students and Concert Tickets Innate understanding of concurrency helps beginners solve CS mechanis

helps beginners solve CS problems with multiple processes executing at the same time.

By Gary Lewandowski, Dennis J. Bouvier, Tzu-Yi Chen, Robert McCartney, Kate Sanders, Beth Simon, and Tammy VanDeGrift

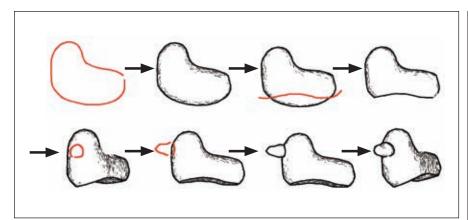

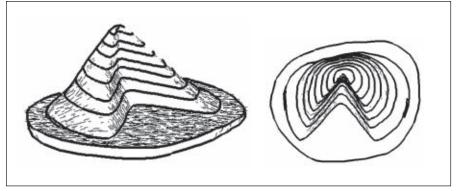

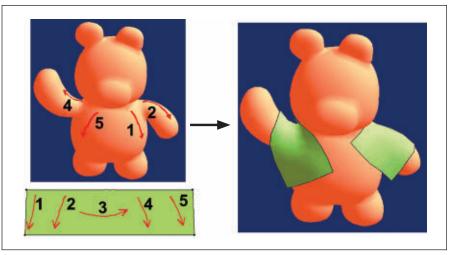

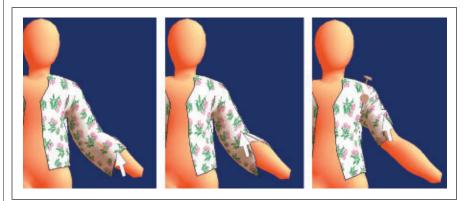

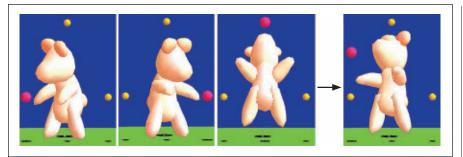

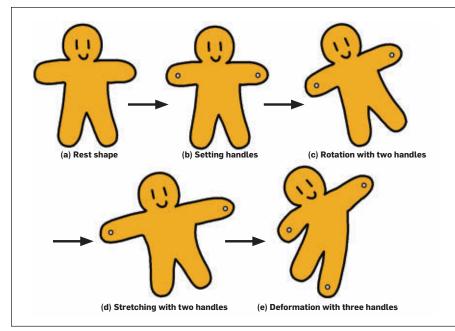

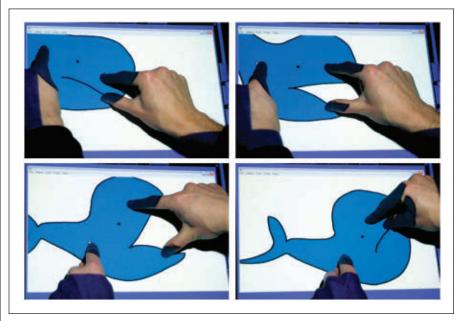

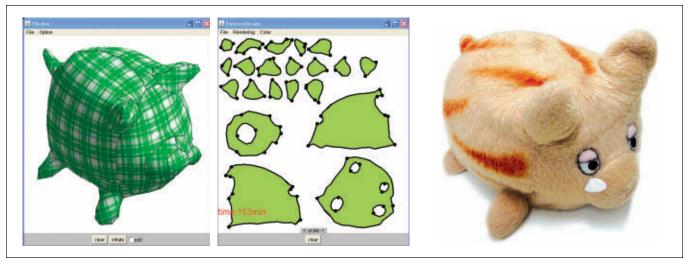

71 **Computer Graphics for All** Interactive computer graphics would rival word-processing and presentation programs for everyday communications. *By Takeo Igarashi*

#### **Research Highlights**

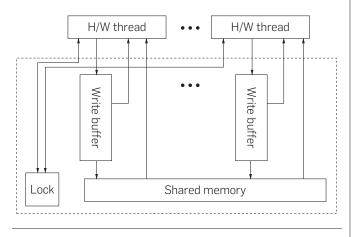

88 Technical Perspective A Solid Foundation for x86 Shared Memory By Hans-J. Boehm

89 x86-TSO: A Rigorous and Usable Programmer's Model for x86 Multiprocessors By Peter Sewell, Susmit Sarkar, Scott Owens, Francesco Zappa Nardelli, and Magnus O. Myreen

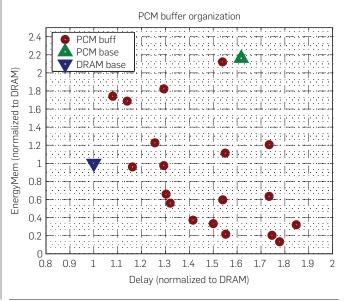

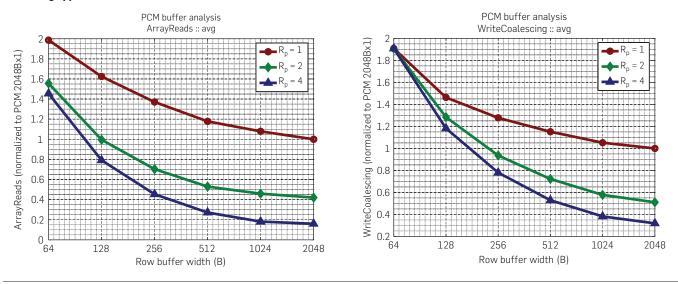

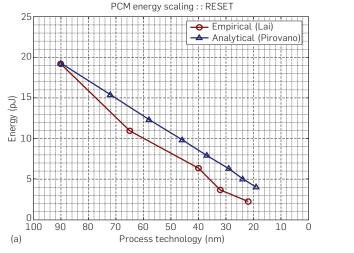

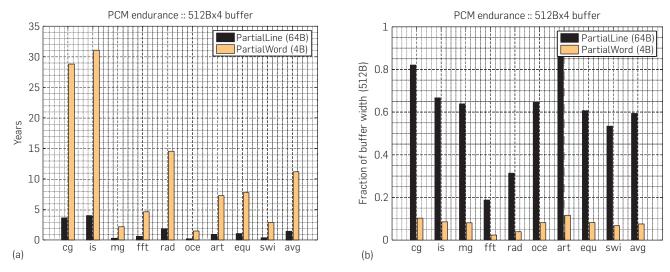

- 98 Technical Perspective Technology Scaling Redirects Main Memories By Mary Jane Irwin

- 99Phase Change Memory Architecture<br/>and the Quest for ScalabilityBy Benjamin C. Lee, Engin Ipek,<br/>Onur Mutlu, and Doug Burger

#### Virtual Extension

As with all magazines, page limitations often prevent the publication of articles that might otherwise be included in the print edition. To ensure timely publication, ACM created *Communications*' Virtual Extension (VE).

VE articles undergo the same rigorous review process as those in the print edition and are accepted for publication on their merit. These articles are now available to ACM members in the Digital Library.

> IT Programs in High Schools: Lessons from the Cisco Networking Academy Program Alan R. Dennis, Thomas M. Duffy, and Hasan Cakir

**Creating the Experience Economy in E-Commerce** *Wei-Lun Chang, Soe-Tsyr Yuan, and Carol W. Hsu*

How Distributed Data Mining Tasks Can Thrive as Knowledge Services Domenico Talia and Paolo Trunifo

ERP: Drilling for Profit in the Oil and Gas Industry Jorge A. Romero, Nirup Menon, Rajiv D. Banker, and Mark Anderson

Why Do People Tag? Motivations for Photo Tagging Oded Nov and Chen Ye

Using ESI Discovery Teams to Manage Electronic Data Discovery John C. Ruhnka and John W. Bagby

Application Service Providers: Market and Adoption Decisions Yurong Yao, Edward Watson, and Beverly K. Kahn

Association for Computing Machinery Advancing Computing as a Science & Profession

### COMMUNICATIONS OF THE ACM

Trusted insights for computing's leading professionals.

Communications of the ACM is the leading monthly print and online magazine for the computing and information technology fields. Communications is recognized as the most trusted and knowledgeable source of industry information for today's computing professional. Communications brings its readership in-depth coverage of emerging areas of computer science, new trends in information technology, and practical applications. Industry leaders use Communications as a platform to present and debate various technology implications, public policies, engineering challenges, and market trends. The prestige and unmatched reputation that Communications of the ACM enjoys today is built upon a 50-year commitment to high-quality editorial content and a steadfast dedication to advancing the arts, sciences, and applications of information technology.

#### STAFF

ACM, the world's largest educational

and scientific computing society, delivers

resources that advance computing as a

science and profession. ACM provides the

profession with leading-edge publications,

conferences, and career resources.

Deputy Executive Director and COO

Director, Office of Financial Services

Director, Office of Membership

Director, Office of SIG Services

Donna Cappo Director, Office of Publications

Director, Office of Group Publishing

Director, Office of Information Systems

**Executive Director and CEO**

John White

Patricia Ryan

Wayne Graves

Russell Harris

Lillian Israel

**Bernard Rous**

Scott Delman

President

Wendy Hall

Vice-President

Alain Chesnais

Barbara Ryder

Past President

Alexander Wolf

Carlo Ghezzi;

Kelly Lyons;

Bruce Maggs

Mary Lou Soffa:

Joseph A. Konstan;

Robert A. Walker;

**Board Members**

Chris Stephenson

Executive Director

Jack Davidson

Anthony Joseph;

Mathai Joseph;

Stuart I. Feldman

Chair, SGB Board

Members-at-Large

Co-Chairs, Publications Board

Ronald Boisvert, Holly Rushmeier

Fei-Yue Wang SGB Council Representatives

PUBLICATIONS BOARD

**Co-Chairs** Ronald F. Boisvert and Holly Rushmeier

Jack Davidson; Nikil Dutt; Carol Hutchins;

Ee-Peng Lim; Catherine McGeoch;

Mary Lou Soffa; Ricardo Baeza-Yates

T (202) 659-9711; F (202) 667-1066

**Computer Science Teachers Association**

M. Tamer Ozsu; Vincent Shen;

ACM U.S. Public Policy Office

Cameron Wilson, Director 1828 L Street, N.W., Suite 800

2 Penn Plaza, Suite 701 New York, NY 10121-0701 USA

Washington, DC 20036 USA

Secretary/Treasurer

ACM COUNCIL

computing field's premier Digital Library and serves its members and the computing

#### DIRECTOR OF GROUP PUBLISHING Scott E. Delman publisher@cacm.acm.org

Executive Editor Diane Crawford Managing Editor Thomas E. Lambert Senior Editor Andrew Rosenbloom Senior Editor/News Jack Rosenberger Web Editor David Roman Editorial Assistant Zarina Strakhan Rights and Permissions Deborah Cotton

Art Director Andrij Borys Associate Art Director Alicia Kubista Assistant Art Director Mia Angelica Balaquiot Production Manager Lynn D'Addesio Director of Media Sales Jennifer Ruzicka Marketing & Communications Manager Brian Hebert Public Relations Coordinator Virgina Gold **Publications Assistant** Emily Eng

#### Columnists

Alok Aggarwal; Phillip G. Armour; Martin Campbell-Kelly; Michael Cusumano; Peter J. Denning; Shane Greenstein; Mark Guzdial; Peter Harsha; Leah Hoffmann; Mari Sako; Pamela Samuelson; Gene Spafford; Cameron Wilson

#### CONTACT POINTS

Copyright permission permissions@cacm.acm.org Calendar items calendar@cacm.acm.org Change of address acmcoa@cacm.acm.org Letters to the Editor Letters@cacm.acm.org

WEB SITE http://cacm.acm.org

#### AUTHOR GUIDELINES http://cacm.acm.org/guidelines

#### ADVERTISING

ACM ADVERTISING DEPARTMENT 2 Penn Plaza, Suite 701, New York, NY 10121-0701 7 (212) 869-7440 F (212) 869-0481

Director of Media Sales Jennifer Ruzicka jen.ruzicka@hq.acm.org

Media Kit acmmediasales@acm.org

#### EDITORIAL BOARD

EDITOR-IN-CHIEF Moshe Y. Vardi eic@cacm.acm.org

NEWS Co-chairs Marc Najork and Prabhakar Raghavan Board Members Brian Bershad; Hsiao-Wuen Hon; Mei Kobayashi; Rajeev Rastogi; Jeannette Wing

#### VIEWPOINTS

**Co-chairs** Susanne E. Hambrusch; John Leslie King; J Strother Moore

Board Members P. Anandan; William Aspray; Stefan Bechtold; Judith Bishop; Stuart I. Feldman; Peter Freeman; Seymour Goodman; Shane Greenstein; Mark Guzdial; Richard Heeks; Rachelle Hollander; Richard Ladner; Susan Landau; Carlos Jose Pereira de Lucena; Beng Chin Ooi; Loren Terveen

#### PRACTICE

Chair Stephen Bourne Board Members

Eric Allman; Charles Beeler; David J. Brown; Bryan Cantrill; Terry Coatta; Mark Compton; Stuart Feldman; Benjamin Fried; Pat Hanrahan; Marshall Kirk McKusick; George Neville-Neil; Theo Schlossnagle; Jim Waldo

The Practice section of the CACM Editorial Board also serves as the Editorial Board of acmqueue.

#### CONTRIBUTED ARTICLES Co-chairs

Al Aho and Georg Gottlob Board Members

Yannis Bakos; Gilles Brassard; Alan Bundy; Peter Buneman; Ghezzi Carlo; Andrew Chien; Anja Feldmann; Blake Ives; James Larus; Igor Markov; Gail C. Murphy; Shree Nayar; Lionel M. Ni; Sriram Rajamani; Jennifer Rexford; Marie-Christine Rousset; Avi Rubin; Abigail Sellen; Ron Shamir; Marc Snir; Larry Snyder; Veda Storey; Manuela Veloso; Michael Vitale; Wolfgang Wahlster; Andy Chi-Chih Yao; Willy Zwaenepoel

#### RESEARCH HIGHLIGHTS Co-chairs

David A. Patterson and Stuart J. Russell Board Members Martin Abadi; Stuart K. Card; Jon Crowcroft; Shafi Goldwasser; Monika Henzinger; Maurice Herlihy; Norm Jouppi; Andrew B. Kahng; Gregory Morrisett; Michael Reiter; Mendel Rosenblum; Ronitt Rubinfeld; David Salesin; Lawrence K. Saul; Guy Steele, Jr.; Gerhard Weikum; Alexander L. Wolf; Margaret H. Wright

#### WEB Co-chairs

Marti Hearst and James Landay Board Members Jason I. Hong; Jeff Johnson; Greg Linden; Wendy E. MacKay

#### ACM Copyright Notice

Copyright © 2010 by Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and full citation on the first page. Copyright for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or fee. Request permission to publish from permissions@acm.org or fax (212) 869-0481.

For other copying of articles that carry a code at the bottom of the first or last page or screen display, copying is permitted provided that the per-copy fee indicated in the code is paid through the Copyright Clearance Center; www.copyright.com.

#### Subscriptions

An annual subscription cost is included in ACM member dues of \$99 (\$40 of which is allocated to a subscription to *Communications*); for students, cost is included in \$42 dues (\$20 of which is allocated to a *Communications* subscription). A nonmember annual subscription is \$100.

#### ACM Media Advertising Policy

Communications of the ACM and other ACM Media publications accept advertising in both print and electronic formats. All advertising in ACM Media publications is at the discretion of ACM and is intended to provide financial support for the various activities and services for ACM members. Current Advertising Rates can be found by visiting http://www.acm-media.org or by contacting ACM Media Sales at (212) 626-0654.

#### Single Copies

Single copies of *Communications of the ACM* are available for purchase. Please contact acmhelp@acm.org.

#### COMMUNICATIONS OF THE ACM

(ISSN 0001-0782) is published monthly by ACM Media, 2 Penn Plaza, Suite 701, New York, NY 10121-0701. Periodicals postage paid at New York, NY 10001, and other mailing offices.

#### POSTMASTER

Printed in the U.S.A.

Please send address changes to *Communications of the ACM* 2 Penn Plaza, Suite 701 New York, NY 10121-0701 USA

WAGHLY

(ACM) 2 Penn Plaza, Suite 701 New York, NY 10121-0701 USA T (212) 869-7440; F (212) 869-0481

T (800) 401-1799; F (541) 687-1840

Association for Computing Machinery

#### DOI: 10.1145/1785414.1785415

# Hypercriticality

### In the two years since we launched the revitalized *Communications of the ACM*, I have received hundreds of email messages from readers. The feedback has been

mostly, but not universally, positive. Many people do note places where we can do better. Some readers point out errors in published articles. Nothing in life is perfect. *Communications* is an ongoing project; continuous improvement is the name of the game.

At the same time, I have also received a fair number of notes with nothing short of withering criticism. For example, six issues into the revitalized *Communications*, I received this comment from a leading computer scientist: "Although I have looked at every issue and at least glanced at every article, I have not yet found one good one."

Do you find this statement harsh? It surely pales in comparison to this: "The level is unbelievably poor. It reads sometimes like a PR article for big companies. Donation to the ACM seems to be the main reviewing criterion. I would call the policy of ACM scientific prostitution, and I don't want to pay for a prostitute."

I believe most of us have received at some point very harsh reviews though, hopefully, not that harsh—on papers or proposals we have written. If you are an experienced researcher, you have undoubtedly dealt with papers and proposals being declined. Still, the harsh tone of negative reviews can be quite unsettling even to experienced authors. When I talk to colleagues about this, they just shrug, but I think this phenomenon, which I call "hypercriticality," deserves our collective attention. Other people recently commented on this issue. In the context of proposal reviewing, Ed Lazowska coined the phrase "circling the wagons and shooting inwards," and John L. King, in a recent CCC blog, referred to such verbal assaults as "Fratricide." Jeff Naughton, referring to conference paper reviewing, said in a recent invited talk that "bad reviewing" is "sucking the air out of our community."

The "hypercriticality" claim is not just based on anecdotes; we actually have data that supports it. Proposals submitted to the Computer and Information Science and Engineering (CISE) Directorate of the U.S. National Science Foundation (NSF) are rated, on the average, close to 0.4 lower (on a 1-to-5 scale) than the average NSF proposal. In his blog entry, King discussed the harmful effects of such harshness.

What is the source of this harshness within our discipline? Here one can only speculate. Let me offer two possible explanations. My first theory refers to the intrinsic nature of our discipline. Computing systems are notoriously brittle. Mistyping one variable

# What is the source of this harshness within our discipline?

#### Moshe Y. Vardi

name can lead to a catastrophic failure. Computing embodies the principle of "For lack of a nail, the kingdom was lost." This makes us eternally vigilant, looking for the slightest flaw. In our eternal hunt for flaws, we often focus on the negative and lose perspective of the positive.

My second theory refers to the sociology of our field. We typically publish in conferences where acceptance rates are 1/3, 1/4, or even lower. Reviewers read papers with "reject" as the default mode. They pounce on every weakness, finding justification for a decision that, in some sense, has already been made. It is particularly easy to be harsh when reviewing proposals. If the proposal is not detailed enough, then the proposer "does not have a clear enough plan of research," but if the proposal is rich in detail, then "it is clear that the proposer has already done the work for which funding is sought."

What is to be done? Remember, we are the authors and we are the reviewers. It is not "them reviewers;" it is "us reviewers." Hillel the Elder, a Jewish scholar, 30 B.C.-10 A.D., said "What is hateful to you, do not do to your fellow." This is known as the Silver Rule in moral philosophy. The Golden Rule, which strengthens the Silver Rule, asserts "do unto others as you would have them do to you." Allow me to rephrase this as the Golden Rule of Reviewing: "Write a review as if you are writing it to yourself." This does not mean that we should not write critical reviews! But the reviews we write must be fair, weighing both strengths and weaknesses; they must be constructive, suggesting how the weaknesses can be addressed; and, above all, they must be respectful.

After all, these are the reviews that we would like to receive!

Moshe Y. Vardi, EDITOR-IN-CHIEF

#### DOI:10.1145/1785414.1785417

### Don't Ignore Security Offshore, or in the Cloud

OSHE Y. VARDI'S Editor's Letter "Globalization and Offshoring of Software Revisited" and Dave Durkee's "Why Cloud Computing Will Never Be Free" (both May 2010) failed to address security risks. Vardi's headline promised an update on the questions raised by increased globalization of outsourced software development. Though I knew his main focus was on the economic impact of global outsourcing, I was still disappointed there was no mention of the security challenges posed by the global supply chain for software. Such challenges have prompted the U.S. Departments of Defense and Homeland Security, the SAFECode consortium, and numerous other organizations to commit significant effort to combating threats posed by software of unknown pedigree and provenance, including individual and state-sponsored "insider threats" (such as implanted malicious logic, backdoors, and exploitable vulnerabilities), particularly when developed offshore. See the Government Accountability Office's Defense Acquisitions: Knowledge of Software Suppliers Needed to Manage Risks (http://www. gao.gov/new.items/d04678.pdf) and the Report of the Defense Science Board Task Force on Mission Impact of Foreign Influence on DOD Software (http://www. acq.osd.mil/dsb/reports/ADA486949.pdf). Though both focus on software used by DoD, the security issues apply to any organization that relies on outsourced software for critical business or mission functions.

Meanwhile, in an otherwise admirable assessment of the strengths and weaknesses of the cloud computing model of outsourced IT-as-a-service, Durkee likewise failed to mention potential consequences of cloud providers not protecting outsourced computing infrastructure against hackers and malicious code. For example, when discussing transparency, he overlooked the fact that no cloud provider allows its customers to implement intrusion detection or security monitoring extending into the management-services layer behind virtualized cloud instances. Moreover, these customers have learned not to expect their providers to deliver detailed security-incident, vulnerability, or malware reports.

The management-service layer provides a back channel through which the content of each cloud instance is accessible, not only by providers, but by any attacker able to hack into or implant a kernel-level rootkit. Once "in," the attacker is positioned to exploit the back channel to manipulate or even make full copies of all cloud instances hosted on the compromised platform. Even if customers manage to get their providers to agree to servicelevel agreements (SLAs) sti pulating a high level of vigilance, reporting, and protection below the cloud-instance layer, the management-services layer remains an inherent weakness that should concern anyone looking to host "in the cloud" the kinds of critical applications Durkee explored.

Karen Mercedes Goertzel, Falls Church, VA

#### Author's Response:

I strongly agree with Goertzel's sentiment and appreciate her raising this very important issue. The executive summary of the 2006 Globalization and Offshoring Report said: "Offshoring magnifies existing risks and creates new and often poorly understood or addressed threats to national security, business property and processes, and individuals' privacy. While it is unlikely these risks will deter the growth of offshoring, businesses and nations should employ strategies to mitigate them." The Report's Chapter 6, "Offshoring: Risks And Exposures," covered the risks at length.

Moshe Y. Vardi, Editor-in-Chief

#### **Author's Response:**

As with performance and uptime, cloud security is determined by the necessity of meeting the terms of SLAs as demanded by customers. As they mature, they will demand even more from their providers' SLAs by agreeing to industry-standard audits and certifications that ensure they get the security they need, a topic that is a great starting point for another article. **Dave Durkee,** Mountain View, CA

Up in the Air

Describing the network effects of a cloud strategy, particularly when it involves SaaS platform efficiency, in his "Technology Strategy and Management" Viewpoint "Cloud Computing and SaaS as New Computing Platforms" (Apr. 2010), Michael Cusumano said that major cloud hosts, including Amazon, Google, and Salesforce, generally rely on detailed SLAs to guarantee security and other parameters for their hosted customers. However, many such hosts, including Amazon SimpleDB and Google Apps, agree to SLAs involving only, perhaps, performance degradation limits and availability of a given service. If cloud-related SLAs fail to include more specific parameters, the cloud infrastructure risks closing itself to new, innovative services due to its lack of dependable guarantees.

Burkhard Stiller and Guilherme Machado, Zürich, Switzerland

#### **Diversity Factor**

Richard Tapia's inspiring Viewpoint "Hiring and Developing Minority Faculty at Research Universities" (Mar. 2010) said that looking for the next Gauss or Turing is not necessarily the key criterion in all CS faculty searches. I have sometimes sensed confusion between the notion that research excellence drives academic success (it does and should) and what might be called the "additive argument," or belief that maximizing the potential research stature of every new hire automatically maximizes a department's overall excellence in research. I read Tapia's section on reexamining search criteria to mean this is not always the case. I concur, convinced that the effects of talent are not simply additive.

It ought to go without saying that the goal of diversity of gender or ethnic origin does not generally conflict with excellence in research. For instance, in recent years my department has interviewed several women candidates who were uniformly superior to their male counterparts.

However, in specific faculty searches it may be that the potential research stature of a certain white male candidate is perceived as exceeding that of a certain female or minority candidate. The latter may be stellar, but the former's intellectual light shines just a bit brighter. If the discrepancy is comparable to the rather high level of uncertainty inherent in measuring a candidate's potential, some may invoke the additive argument.

However, this argument seems to rest on two questionable assumptions: departmental excellence (however measured) is the arithmetic sum of the individual levels of excellence of its faculty members; and the success of an individual researcher is independent of the surrounding environment.

Both are wrong. Excellence in research (individually or across a department) is a nonlinear function of interdependent factors. For instance, in a department that makes itself attractive to a broader pool of graduate students through the composition of its faculty, all researchers benefit from the resulting potentially improved quality of the department's student body. This also holds when attracting new colleagues, including so-called superstars. When female or minority candidates are at, say, the top of the list in a particular search, they (like everybody else) also consider a department's environment when choosing which job offer to accept. Moreover, a more welcoming, collegial, diverse faculty often leads to better and more frequent collaboration, as well as to more vibrant research.

The question is not whether to compromise between excellence and diversity but how best to foster excellence, with diversity a part of the equation.

Carlo Tomasi, Durham, NC

#### Wrong Side of the Road

In his Editor's Letter "Revisiting the Publication Culture in Computing Research" (Mar. 2010), Moshe Y. Vardi said computer science is "the only scientific community that considers conference publications as the primary means of publishing our research results," asking, "Why are we the only discipline driving on the conference side of the 'publication road?'"

As an old timer, I can say that in the early days, there was a belief (conceit might be a better word) that the field's pace of discovery was happening so quickly that only conferences, with subsequent prompt publication of proceedings, could communicate results in a timely manner. As a corollary, the traditional peer-reviewed published literature review fell behind, as it was relieved of temporal pressure through the published proceedings.

These days, the pace of discovery in the biological sciences, including molecular biology, genomics, and proteomics, far exceeds that of computer science. Yet the gold standard of publication in archival journals continues. It is the ultimate irony that computer science, along with various disciplines in the physical sciences, employs the tools developed by computer scientists to ensure timely dissemination of research results through the online editions of their publications. Science, Nature, Cell, and other leading journals routinely present their most important articles in online form first. If, perhaps, computer science would make greater use of its own tools, the shoemaker's children would no longer go barefoot, and published proceedings would fade into its proper historical niche.

Stuart Zimmerman, Houston, TX

**More to Celebrate in RDBMS History** Gary Anthes offered good reporting but also some serious errors concerning pre-RDBMS history in his news article "Happy Birthday, RDBMS!" (May 2010), saying "In 1969, an ad hoc consortium called CODASYL proposed a hierarchical database model built on the concepts behind IMS. CODASYL claimed that its approach was more flexible than IMS, but it still required programmers to keep track of far more details than the relational model did."

Please compare with the following basic facts as reported in Wikipedia: "In 1965 CODASYL formed a List Processing Task Force. This group was chartered to develop COBOL language extensions for processing collections of records; the name arose because Charles Bachman's IDS system (which was the main technical input to the project) managed relationships between records using chains of pointers. In 1967 the group renamed itself the Data Base Task Group and in October 1969 published its first language specifications for the network database model, which became generally known as the CODASYL Data Model."

The Integrated Data Store (IDS) has been in continuous productive use since 1964, running first on GE 200 computers. In 1966, it began supporting a nationwide, 24/7, order-entry system (OLTP). And in 1969, running on the GE 600, it began supporting a shared-access (OLTP) database, complete with locks, deadlock detection, and automatic recovery and restart.

IBM did not release its IMS/360 (Information Management System) based on the hierarchical data model until September 1969 when future relational databases were still just a gleam in Ted Codd's eye.

B.F. Goodrich received the IDS source code from GE in 1964, renaming it the Integrated Database Management System, or IDMS, when rewritten for the IBM 360 (1969–1971). IDMS was acquired (1973) and marketed worldwide by Cullinane (later Cullinet). IDMS was acquired (1989) by CA (formerly Computer Associates), which still actively supports it worldwide on more than 4,000 IBM mainframes. British Telecom and the Brazilian government are the best-known IDMS users, rated, in 2005, the second- and thirdlargest OLTP systems in the world.

For more, please see the refereed papers on IDS, IMS, IDMS, and other DBMS products in *IEEE Annals of the History of Computing* (Oct.–Dec. 2009) special issue on "Mainframe Software: Database Management Systems." A future issue is planned to cover more recent RDBMS history.

**Charles W. (Charlie) Bachman**, Lexington, MA, ACM Turing Award 1973

© 2010 ACM 0001-0782/10/0700 \$10.00

**Communications** welcomes your opinion. To submit a Letter to the Editor, please limit your comments to 500 words or less and send to letters@cacm.acm.org.

| Association for<br>Computing Machinery                                                                                                                                                                                                                                                                                                                                         | embership                                                                                                                                                                                                                                                                                                                |                                                                                |                                                |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|--|

| Advancing Computing as a Science & Profession                                                                                                                                                                                                                                                                                                                                  | digital library order form                                                                                                                                                                                                                                                                                               |                                                                                |                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          |                                                                                | Priority Code: ACA                             |  |

| You can join                                                                                                                                                                                                                                                                                                                                                                   | ACM in several e                                                                                                                                                                                                                                                                                                         | asy ways:                                                                      |                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                | <b>Phone</b><br>0-342-6626 (US & Canada)<br>212-626-0500 (Global)                                                                                                                                                                                                                                                        |                                                                                | <b>Fax</b><br>12-944-1318                      |  |

| Or, complete this applica                                                                                                                                                                                                                                                                                                                                                      | ation and return with pa                                                                                                                                                                                                                                                                                                 | yment via posta                                                                | l mail                                         |  |

| Special rates for residents of developing cour<br>http://www.acm.org/membership/L2-3/                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                          | <b>tes for members</b><br>ww.acm.org/memb                                      | of sister societies:<br>bership/dues.html      |  |

| Name<br>Address                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>Purposes of ACM</li> <li>ACM is dedicated to:</li> <li>1) advancing the art, science, engineering, and application of information technology</li> <li>2) fostering the open interchange of information to serve both professionals and the public</li> <li>3) promoting the highest professional and</li> </ul> |                                                                                |                                                |  |

| City State/Province                                                                                                                                                                                                                                                                                                                                                            | Postal code/Zip                                                                                                                                                                                                                                                                                                          | ethics standards                                                               |                                                |  |

| Country E-mail address                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                          | l agree with the Pu                                                            | arposes of ACM:                                |  |

| Area code & Daytime phone Fax                                                                                                                                                                                                                                                                                                                                                  | Member number, if applicable                                                                                                                                                                                                                                                                                             | http://www.ac                                                                  | 1 Code of Ethics:<br>m.org/serving/ethics.html |  |

| PROFESSIONAL MEMBERSHIP:                                                                                                                                                                                                                                                                                                                                                       | STUDENT ME                                                                                                                                                                                                                                                                                                               | MBERSHIP:                                                                      |                                                |  |

| ACM Professional Membership: \$99 USD                                                                                                                                                                                                                                                                                                                                          | ACM Student Mem                                                                                                                                                                                                                                                                                                          | ACM Student Membership: \$19 USD                                               |                                                |  |

| ACM Professional Membership plus the ACM Digital Libr                                                                                                                                                                                                                                                                                                                          | ary: 🔲 ACM Student Memb                                                                                                                                                                                                                                                                                                  | ACM Student Membership plus the ACM Digital Library: \$42 USD                  |                                                |  |

| \$198 USD (\$99 dues + \$99 DL)                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          | ACM Student Membership PLUS Print CACM Magazine: \$42 USD                      |                                                |  |

| ACM Digital Library: \$99 USD (must be an ACM member                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                          | ACM Student Membership w/Digital Library PLUS Print<br>CACM Magazine: \$62 USD |                                                |  |

| All new ACM members will receive an<br>ACM membership card.<br>For more information, please visit us at www.acm.org<br>Professional membership dues include \$40 toward a subscrip<br>to <i>Communications of the ACM</i> . Member dues, subscriptions,<br>and optional contributions are tax-deductible under certain<br>circumstances. Please consult with your tax advisor. | money order, make<br>currency at current                                                                                                                                                                                                                                                                                 | exchange rate.                                                                 | in US dollars or foreign                       |  |

| RETURN COMPLETED APPLICATION TO:                                                                                                                                                                                                                                                                                                                                               | 🖵 ACM Digital Library                                                                                                                                                                                                                                                                                                    | (\$99)                                                                         | \$                                             |  |

| Association for Computing Machinery, Inc.                                                                                                                                                                                                                                                                                                                                      | 🗖 Student Member D                                                                                                                                                                                                                                                                                                       |                                                                                | \$                                             |  |

| General Post Office                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                          | Total Amount Due                                                               | \$                                             |  |

Card #

P.O. Box 30777

New York, NY 10087-0777

Questions? E-mail us at acmhelp@acm.org Or call +1-800-342-6626 to speak to a live representative

**Satisfaction Guaranteed!**

Expiration date

Signature

#### DOI: 10.1145/1785414.1785418

### **In the Virtual Extension**

Communications' Virtual Extension brings more quality articles to ACM members. These articles are now available in the ACM Digital Library.

#### IT Programs in High Schools: Lessons from the Cisco Networking Academy Program

Alan R. Dennis, Thomas M. Duffy, and Hasan Cakir

The authors studied 5,392 students taking a course from the Cisco Networking Academy at 764 high schools across the U.S. to understand the factors that influenced their achievement and confidence. Surprisingly, school characteristics (inner city vs. suburban, rich vs. poor) had virtually no impact. What mattered most was instruction quality and an individual student's ability, motivation, and, unfortunately, gender. This style of program, with a strong centralized curriculum, local customization, standards-based testing, and strong teacher support overcame the traditional educational barriers to enable each student to rise to his or her own level of ability and motivation.

#### **Creating the Experience Economy in E-Commerce**

Wei-Lun Chang, Soe-Tsyr Yuan, and Carol W. Hsu

The potential economic value of experience-oriented offerings has been demonstrated in the physical marketplace. This study suggests the widespread use of the Internet allows the experience economy to be extended to the virtual marketplace. The growing practice of online collaborative design demonstrates the potential for providing the experience economy via the Internet. The authors propose expanding the existing practices by incorporating the concept of collaborative pricing into the design of experience offerings, as demonstrated in their iCare platform. The article is intended to motivate further research into the development of the experience economy in e-commerce.

#### How Distributed Data Mining Tasks Can Thrive as Knowledge Services

Domenico Talia and Paolo Trunifo

Through a service-oriented approach we can support distributed business intelligence tasks in clouds and grids. Those services can implement all the tasks in data mining and in knowledge discovery processes such as data selection, data analysis, and knowledge representation. The authors explore architectures and services for distributed knowledge discovery such as the Knowledge Grid, the Weka4WS toolkit, and mobile data mining services. The article describes a strategy and a model based on the use of services for the design of distributed knowledge discovery applications and discusses how grid and cloud frameworks can be developed as a collection of services and how they can be used to support knowledge discovery processes using the SOA model.

### ERP: Drilling for Profit in the Oil and Gas Industry

Jorge A. Romero, Nirup Menon, Rajiv D. Banker, and Mark Anderson

The article presents research that applies to a new approach toward understanding ERP implementation. Rather than looking at ordinary measures of firm performance, the authors examine strategic performance measures that can only be utilized if one delves into data that is not found on the financial statements. It is one of the first studies to show the sources of profitability after an ERP implementation and will help managers understand the strategic and managerial implications of ERP implementation.

#### Why Do People Tag? Motivations for Photo Tagging

Oded Nov and Chen Ye

Given the growing popularity of tags as a means of sharing and organizing large amounts of data, it is critical for developers and managers of collaborative content-sharing systems such as Flickr, YouTube, and del.icio.us to understand what motivates users to tag. The authors examine individual-level motivations using a newly developed scale as well as the social presence driver and the number of user photos. The findings suggest that both social presence and individual-level motivation affect users' tagging level.

#### Using ESI Discovery Teams to Manage Electronic Data Discovery

#### John C. Ruhnka and John W. Bagby

Many organizations face litigation threats with associated crippling costs, staff-time demands, and adverse financial impacts. "Discovery," the legal and operational process governing the evidentiary use of electronically stored information (ESI)including email messages-plays a central role in the cost of litigation as well as in potential outcomes. Multidiscipline ESI "discovery teams" containing key IT, legal, and operational players involved in this complex process can more effectively manage the "litigation hold" process, and can better assess the potential costs of alternative strategies in collection, identification, verification, recovery, and production of relevant electronic data sought as evidence.

#### Application Service Providers: Market and Adoption Decisions

Yurong Yao, Edward Watson, and Beverly K. Kahn

Deciding whether, how, and with whom to outsource an organization's applications is important. Key factors influence the Application Service Provider (ASP) decision-making process and the ultimate organizational success. The authors examine the current ASP market and recommend evaluation criteria by looking at hosting by "Pure ASPs" (small companies who purely provide hosting services) and "ISVs" (independent software vendors, who develop software and host their own applications). These ASPs provide either vertical (within a single industry sector) or horizontal (across industries) applications. Several adoption cases are presented to explain the recommendations.

The *Communications* Web site, http://cacm.acm.org, features more than a dozen bloggers in the BLOG@CACM community. In each issue of *Communications*, we'll publish selected posts or excerpts.

### twitter

Follow us on Twitter at http://twitter.com/blogCACM

#### DOI:10.1145/1785414.1785419

#### http://cacm.acm.org/blogs/blog-cacm

### Software Development and Crunch Time; and More

Ruben Ortega discusses developers and crunch time; Mark Guzdial considers the impact of open source practices on computing education; and Daniel Reed writes about the technological shift from computational paucity to computational plethora.

#### Ruben Ortega's "Why Do Software Developers Tolerate 'Crunch Time'?"

http://cacm.acm.org/blogs/ blog-cacm/70922

Given the increased risk of burnout for an extended "crunch time," why do developers put up with it?

For software developers, crunch time is a period prior to a major product milestone when team members are asked to put in extra effort to get a product finished by a specific delivery date. Practically, this can be a horrific period of 80-plus hour weeks that goes on for months as the team scrambles to deal with bugs, last-minute feature requests and modifications, and milestones. For game companies and large Internet retailers in particular, the mantra of "Christmas never slips" means that crunch time occurs during the summer so products can be released by the fall and be available between Thanksgiving and Christmas. Recently, the wives of Rockstar Games posted an open letter to the company's management about the impact of the crunch time on their lives. The company was demanding 6–7 days a week, with 12–16 hour days. The impact included mental, physical, and emotional strain on the employees and their families.

Reading the discussions on Slashdot about Rockstar Games' working conditions highlighted that this problem is industrywide. As a developer and manager, I have worked on a number of projects at various startups that involved periods of crunch time that lasted longer than I thought was realistic. When I was a young engineer working on Amazon Auctions, doing the all-nighter was a badge of honor. Eventually, I discovered most of the code you write during those A.м. hours will likely be thrown away. After a few crunch times. I learned to be a better self-advocate, and was able to sensibly set expectations of what combination of features, quality, and testing I could deliver by a given date. When I made the transition from developer to manager, I was glad to have had the experience so I could advocate for my teams. Although I couldn't always get rid of crunch times, I worked to keep their durations as short as possible.

Why do developers put up with crunch time? I believe the reason is as simple as "progress." "Progress" was the factor that was most important to 12,000 workers, according to two researchers who analyzed the workers' diary entries.

As long as the workers believe they are making headway in delivering their product, they are getting an intrinsic reward that motivates them to work more. If you have a team making progress on a delivery, the combined effort of the team will self-reinforce and encourage them all for their efforts. On Amazon Auctions, I worked on implementing search for the system and would nap while another team member would deliver new catalog content. By the time I returned, we would integrate our code, which would result in a complete auction search results. The work was rewarding despite our working through weekends to complete the project. The progress was beautiful and easy to see. One day the system had mockups for search results and the next day the results would be feeding from live data. The intrinsic reward of making progress and working with the team to deliver helped combat the potential for burnout.

It is unrealistic to deliver any project without going through some crunch time. Although progress helps to motivate employees during those periods, ineffective project planning can lead to an egregious amount of time where progress alone will not be enough to sustain the employees' motivation. If excessive crunch time continues to occur, the employees—the company's most valuable resource—should work to either change the organization or they will be compelled to move to a more supportive company. The books *Peopleware* and *Slack: Getting Past Burnout, Busywork and Total Efficiency* are great reminders on why we should work hard to take care of our teams.

#### Mark Guzdial's "The Impact of Open Source on Computing Education"

http://cacm.acm.org/blogs/ blog-cacm/72144

We had a Georgia Tech alum, Mike Terry (now at Waterloo) visit us a couple weeks ago. Mike's research is on usability practices in open source. I got a chance to chat with Mike, and we talked about the impacts of open source on computing education, such as high school students getting started with computing by working in open source development. Overall, though, I came away concerned what the growth of open source development means for the future of computing education.

At a time when we are trying to broaden participation in computing, open source development is even more closed and less diverse than commercial software development. It is overwhelmingly white, Asian, and male. Some estimates suggest that less than 1% of open source developers are female.

Many kids and parents worry that all computer science jobs are being offshored and that it's not worth studying computing. As more and more of the software we use daily is created via open source development, I wonder if kids and parents will hear the message, "Most software developers work for free, or at least have to work for free for years before they can become professional and get paid for their work." Of course, that's not true. Neither is it true that all IT jobs are being offshored, but that's still what some people believe.

One of our challenges in computing education is convincing people that computing is broad and about more than programming. Open source values code above all, or as Linux's originator Linux Torvalds said, "Talk is cheap. Show me the code." We're trying to convince students that talk is *also* valuable in computing.

Finally, Mike's talk was about how common usability practices are rare in open source development. Of course, that's a concern in itself, but it's particularly problematic for newcomers. When students develop toward being professionals, they frequently engage in a process that educators call legitimate peripheral participation (LPP). It's LPP when you start out in a company picking up trash (doing something legitimate on the periphery), and in so doing, figure out what happens in the company. Students can get started in software development at a company by doing tasks that aren't directly about writing software, but are about the whole enterprise. These legitimate peripheral tasks serve as a stepping stone into the process, like writing documentation or running subjects in usability testing. If you don't have usability testing, you don't have that path into the process. Breaking into an open source development process is hard, and that keeps more students out than invites them in.

I wrote on this topic in my regular blog, and was surprised at the response. I learned that it is not acceptable to criticize religion, Santa Claus, or open source development—it's a "good" that should just be accepted as such. I disagree. Open source development does generate enormous good, but it could do *more* good if it improved its practices. It's hard to change open source development, because of its distributed nature. Open source developers should worry about the messages they send future developers, especially if they hope to grow and attract the development talent pool.

#### Daniel Reed's "Paucity to Plethora: Jevons Paradox"

http://cacm.acm.org/blogs/ blog-cacm/72373

Those of us of a certain age remember when the university computer (note the singular) was a scientific and engineering shrine, protected by computer operators and secure doors. We acolytes extended offerings of FORTRAN, ALGOL, or COBOL via punched card decks, hoping for the blessings that accrued from a syntactically correct program that compiled and executed correctly.

The commonality across all our experiences was the need to husband computer time and plan job submissions carefully, particularly when one's job might wait in the queue for six to 10 hours before entering execution. I distinctly remember spending many evenings laboriously examining my latest printout, identifying each syntax error and tracing the program flow to identify as many logic errors as possible before returning to the keypunch room to create a new punched card deck.

Because computing time was scarce and expensive, we devoted considerable human effort to manual debugging and optimization. Today, of course, my wristwatch contains roughly as much computing power as that vintage university mainframe, and we routinely devote inexpensive computing time to minimize human labor. Or do we?

Yes, we routinely use WIMP interfaces for human-computer interaction, cellular telephony is ubiquitous, and embedded computers enhance everyday objects. However, I suspect much of computing is still socially conditioned by its roots in computational paucity to fully recognize the true opportunity afforded by computational plethora.

Many of us are wed to a stimulusresponse model of computing, where humans provide the stimulus and computers respond in preprogrammed ways. In a world of plethora, computing could glean the work, personal, and emotional context, anticipating information queries and computing on behalf rather than in response. My computer could truly become my assistant.

In economics, the Jevons paradox posits that a technological increase in the efficiency with which a resource can be used stimulates greater consumption of the resource. So it is with computing. I believe we are just at the cusp of the social change made possible by our technological shift from computational paucity to computational plethora.

Ruben Ortega is an engineering director at Google. Mark Guzdial is a professor at the Georgia Institute of Technology. Daniel Reed is vice president of Technology Strategy & Policy and the eXtreme Computing Group at Microsoft.

© 2010 ACM 0001-0782/10/0700 \$10.00

DOI:10.1145/1785414.1785420

David Roman

### In Case You Missed It

The most popular content on *Communications*' site is something many readers know nothing about. The BLOG@CACM (http://cacm.acm.org/blogs/blog-cacm) is original online material that does not appear in the monthly magazine except in abbreviated form (see page 10). Eleven entries from this blog were among the site's 100 most popular articles in the first 14 months following its makeover, and seven landed in the top 50 (see below). That's more articles than from any single section of the monthly magazine.

These frontrunners show the strength and diversity of the blogs. Most were penned by regular contributors, but a couple were filed by guest bloggers from a major ACM conference. *Communications* is always looking for new bloggers: guests as well as new experts.

The blogs generate a strong share of comments. In most of the cases cited here, the author is an active participant in the discussions, responding to questions, refining points, and bringing an immediacy and level of engagement the magazine cannot match.

While it is clear that many readers are finding this content, it is also clear that many are not. A recent survey found that 40% of readers didn't know or had no opinion about the BLOG@CACM, and 61% said the same about the site's blogs overall (it also publishes a Blogroll at http://cacm.acm.org/blogs/blogroll). If you are in the 'don't know' category, here's what you've missed. If you are interested in blogging for the BLOG@CACM as a regular contributor or from a conference, email blog@cacm.acm.org.

| Title/URL                                                                                                             | Author/URL                                                                    | # of User<br>Comments |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|

| How We Teach Introductory<br>Computer Science is Wrong<br>http://cacm.acm.org/blogs/blog-cacm/45725                   | Mark Guzdial<br>http://www.cc.gatech.edu/~guzdial/                            | 15                    |

| The End of a DBMS Era (Might Be Upon Us)<br>http://cacm.acm.org/blogs/blog-cacm/32212                                 | Michael Stonebraker<br>http://www.csail.mit.edu/user/1547                     | 6                     |

| The 'NoSQL' Discussion Has Nothing<br>to do With SQL<br>http://cacm.acm.org/blogs/blog-cacm/50678                     | Michael Stonebraker<br>http://www.csail.mit.edu/user/1547                     | 7                     |

| Errors in Database Systems, Eventual<br>Consistency, and the CAP Theorem<br>http://cacm.acm.org/blogs/blog-cacm/83396 | Michael Stonebraker<br>http://www.csail.mit.edu/user/1547                     | 10                    |

| Extreme Agility at Facebook<br>http://cacm.acm.org/blogs/blog-cacm/51564                                              | E. Michael Maximilien<br>http://www.maximilien.com/homepage/<br>about_me.html | 4                     |

| What is a Good Recommendation Algorithm?<br>http://cacm.acm.org/blogs/blog-cacm/22925                                 | Greg Linden<br>http://glinden.blogspot.com/                                   | 10                    |

| Clay Shirky: Doing work, or Doing Work?<br>http://cacm.acm.org/blogs/blog-cacm/72609                                  | Michael Bernstein<br>http://people.csail.mit.edu/msbernst/                    | 4                     |

### ACM Member News

#### ALAIN CHESNAIS ELECTED ACM PRESIDENT

Alain Chesnais, owner of Visual Transitions, a Toronto-based consulting company specializing in

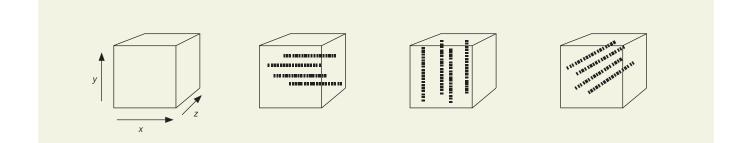

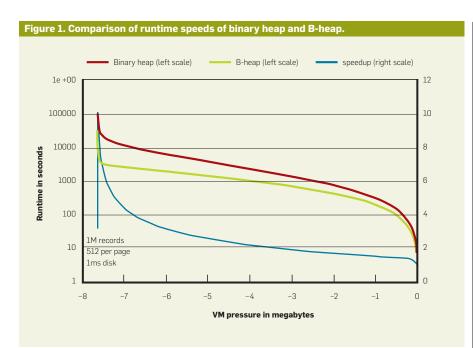

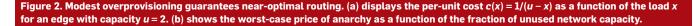

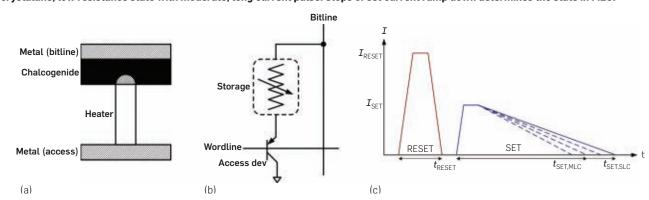

computer graphics and social networks, was elected president of ACM in the May 2010 general election.